如何實現(xiàn)先進晶圓級封裝技術?五大要素即可。

追溯芯片封裝歷史,將單個單元從整個晶圓中切割下來再進行后續(xù)封裝測試的方式一直以來都是半導體芯片制造的“規(guī)定范式”。然而,隨著芯片制造成本的飛速提升以及消費市場對于芯片性能的不斷追求,人們開始意識到革新先進封裝技術的必要性。

對傳統(tǒng)封裝方式的改革創(chuàng)新,促成了晶圓級封裝技術(Wafer Level Package,WLP)的“應運而生”。

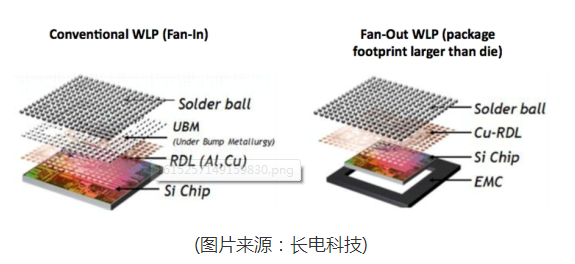

晶圓級封裝技術可定義為:直接在晶圓上進行大部分或全部的封裝、測試程序,然后再進行安裝焊球并切割,產(chǎn)出一顆顆的 IC 成品單元(如下圖所示)。

晶圓級封裝技術與打線型(Wire-Bond)和倒裝型(Flip-Chip)封裝技術相比 ,能省去打金屬線、外延引腳(如QFP)、基板或引線框等工序,所以具備封裝尺寸小、電氣性能好的優(yōu)勢。

封裝行業(yè)的領跑者們大多基于晶圓模式來批量生產(chǎn)先進晶圓級封裝產(chǎn)品,不但可利用現(xiàn)有的晶圓級制造設備來完成主體封裝制程的操作,而且讓封裝結構、芯片布局的設計并行成為現(xiàn)實,進而顯著縮短了設計和生產(chǎn)周期,降低了整體項目成本。

先進晶圓級封裝的主要優(yōu)勢包括:

1. 縮短設計和生產(chǎn)周期,降低整體項目成本;

2. 在晶圓級實現(xiàn)高密度 I/O 互聯(lián),縮小線距;

3. 優(yōu)化電、熱特性,尤其適用于射頻/微波、高速信號傳輸、超低功耗等應用;

4. 封裝尺寸更小、用料更少,與輕薄、短小、價優(yōu)的智能手機、可穿戴類產(chǎn)品達到完美契合;

5. 實現(xiàn)多功能整合,如系統(tǒng)級封裝(System in Package,SiP)、集成無源件(Integrated Passive Devices,IPD)等。

需要強調(diào)的一點是,與打線型封裝技術不同,用晶圓級封裝技術來實現(xiàn)腔內(nèi)信號布線(Internal Signal Routing)有多個選項:晶圓級凸塊(Wafer Bumping)技術、再分布層(Re-Distribution Layer)技術、硅介層(Silicon Interposer)技術、硅穿孔(Through Silicon Via)技術等。

先進晶圓級封裝技術,主要包括了五大要素:

1. 圓級凸塊(Wafer Bumping)技術;

2. 扇入型(Fan-In)晶圓級封裝技術;

3. 扇出型(Fan-Out)晶圓級封裝技術;

4. 2.5D 晶圓級封裝技術(包含IPD);

5. 3D 晶圓級封裝技術(包含IPD)。

作為芯片封裝行業(yè)內(nèi)的先鋒,隨著芯片尺寸和光刻節(jié)點縮小,長電科技正在全面推進晶圓級封裝技術各細分領域的技術研發(fā)。在晶圓級凸塊技術、扇入型晶圓級封裝技術、扇出型晶圓級封裝技術、2.5D 和 3D 晶圓級封裝技術領域,長電科技都有著足夠完善的集成解決方案。

晶圓凸塊(Wafer Bumping),顧名思義,即是在切割晶圓之前,于晶圓的預設位置上形成或安裝焊球(亦稱凸塊)。晶圓凸塊是實現(xiàn)芯片與 PCB 或基板(Substrate)互連的關鍵技術。凸塊的選材、構造、尺寸設計,受多種因素影響,如封裝大小、成本及電氣、機械、散熱等性能要求。

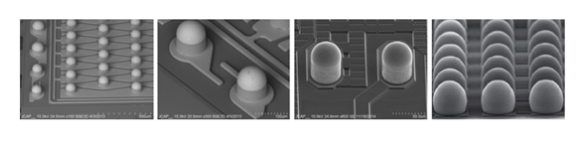

長電科技在晶圓凸點設計和工藝流程等方面具有豐富的經(jīng)驗,業(yè)務涵蓋印刷型凸點(Printed Bump)技術、共晶電鍍型落球(Ball Drop with Eutectic Plating)技術、無鉛合金(Lead-Free Alloy)及銅支柱合金(Copper-Pillar Alloy)凸點技術等,并經(jīng)量產(chǎn)驗證適用于 8 英寸(200mm)和 12 英寸(300mm)大小的標準硅晶圓。下圖所示為幾款典型的晶圓凸塊實例:

扇入型晶圓級封裝(Fan-In Wafer Level Package,F(xiàn)IWLP)技術,業(yè)內(nèi)亦稱晶圓級芯片規(guī)模封裝(Wafer Level Chip Scale Package,WLCSP)技術,是當今各類晶圓級封裝技術中的主力。近兩年,扇入型晶圓級封裝產(chǎn)品的全球出貨量都保持在每年三百億顆以上,主要供給手機、智能穿戴等便攜型電子產(chǎn)品市場。

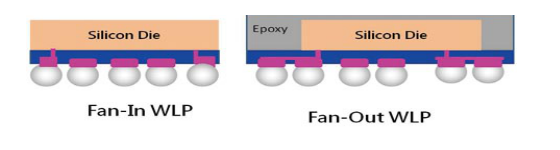

隨著便攜型電子產(chǎn)品的空間不斷縮小、工作頻率日益升高及功能需求的多樣化,芯片輸入/輸出(I/O)信號接口的數(shù)目大幅增加,凸塊及焊球間距(Bump Pitch & Ball Pitch)的精密程度要求漸趨嚴格,再分布層(RDL)技術的量產(chǎn)良率也因此越發(fā)受重視。在這種背景下,扇出型封裝(Fan-Out Wafer Level Package,F(xiàn)OWLP) 及扇入扇出混合型(Hybrid Fan-In/Fan-Out)等高端晶圓級封裝技術應運而生。下圖所示為FIWLP(左)、FOWLP(右)的典型結構:

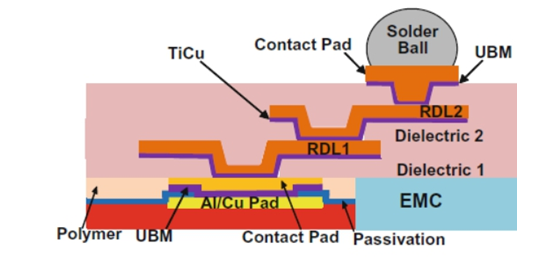

在晶圓級封裝制程里, 再分布層(Re Distribution Layer, RDL)技術主要用于在裸芯(Bare Die)和焊球之間重新規(guī)劃(也可理解為優(yōu)化)信號布線、傳輸?shù)穆窂剑赃_到將晶圓級封裝產(chǎn)品的信號互聯(lián)密度、整體靈活度最大化的目的。RDL 的技術核心,簡單來說就是在原本的晶圓上附加一層或多層的橫向連接,用來傳輸信號。

下圖所示為典型的 Chip-First RDL 方案。值得注意的是,在該方案中有兩層電介質(zhì)(Dielectric)材料,用來保護被其包裹的 RDL 層(可理解為應力緩沖)。另外,凸塊冶金(Under Bump Metallurgy,UBM)技術在這里也派上了用場,來幫助觸點(Contact Pad)支撐焊球、RDL 還有電介質(zhì)。

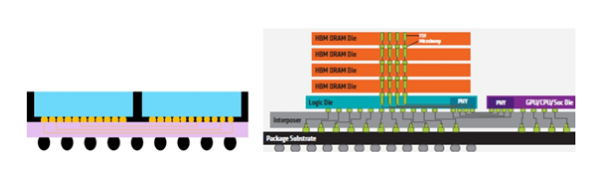

隨著超高密度多芯片模組(Multiple Chip Module,MCM)乃至系統(tǒng)級封裝(SiP)產(chǎn)品在 5G、AI、高性能運算、汽車自動駕駛等領域的普及,2.5D 和 3D 晶圓級封裝技術備受設計人員青睞。下圖所示為 2.5D(左)和 3D(右)晶圓級封裝技術。

如上方圖左所示,對 2.5D 晶圓級封裝技術而言,兩顆芯片的信號互聯(lián),可以通過再分布層(Re-Distribution Layer,RDL)或者硅介層(Silicon Interposer)技術來實現(xiàn)。

如上方圖右所示,對 3D 晶圓級封裝技術而言,邏輯、通訊類芯片如 CPU、GPU、ASIC、PHY 的信號互聯(lián),也可通過再分布層(RDL)或硅介層(Silicon Interposer)技術來實現(xiàn)。但是,3D 堆疊起來的多個高帶寬存儲(High-Bandwidth Memory,HBM)芯片與其底部的邏輯類芯片的信號互聯(lián),則由硅穿孔(Through Silicon Via,TSV)技術來實現(xiàn)。當然,以上幾種互聯(lián)(Interconnect)如何取舍,需根據(jù)實際規(guī)格、成本目標具體問題具體分析。

不論著眼現(xiàn)在,還是放眼未來,隨著 5G、人工智能、物聯(lián)網(wǎng)等大技術趨勢奔涌而至,在高密度異構集成的技術競賽中,晶圓級封裝技術必將占有一席之地。

長電科技也將繼續(xù)推進先進晶圓級封裝技術發(fā)展,通過自身高集成度的先進晶圓級封裝技術與解決方案,滿足全球范圍內(nèi)客戶的多方位需求,推動中國封測產(chǎn)業(yè)向著高質(zhì)量、高端化的目標不斷前行。

- 上一篇:線性霍爾HW-302B的國產(chǎn)替代銻化銦霍爾SNK-302說明 2021/3/11

- 下一篇:集成電路芯片封裝有哪些?芯片組是什么? 2021/3/10